CORGi @ CMU

Computer Organization Research Group led by Prof. Nathan Beckmann

Navigate to

Energy-Minimal Programmable Architectures for Intelligence Beyond the Edge

This project aims to enable a new class of intelligent, ultra-low-power computer systems for the Internet of Things. Future IoT applications will demand intelligence at the edge to avoid expensive and insecure communication with the cloud. These applications run on very low power budgets either due to extend battery life or because systems harvest energy from their environment. Unfortunately, conventional, performance-oriented systems are too inefficient to run sophisticated computation (e.g., machine learning) on the device itself.

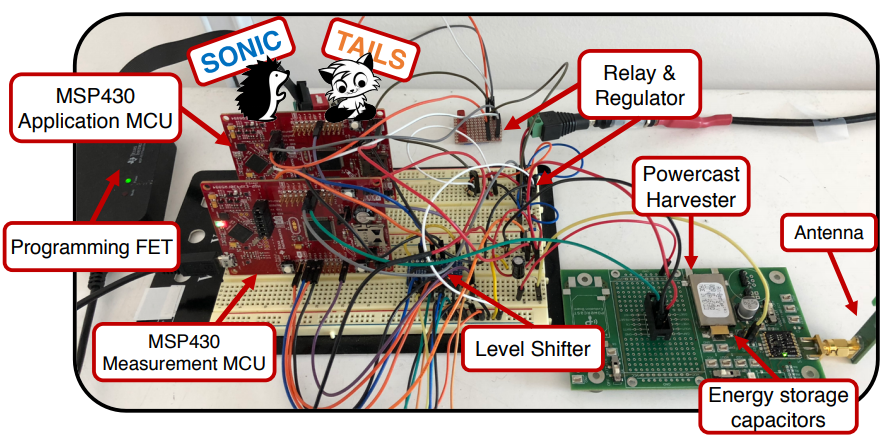

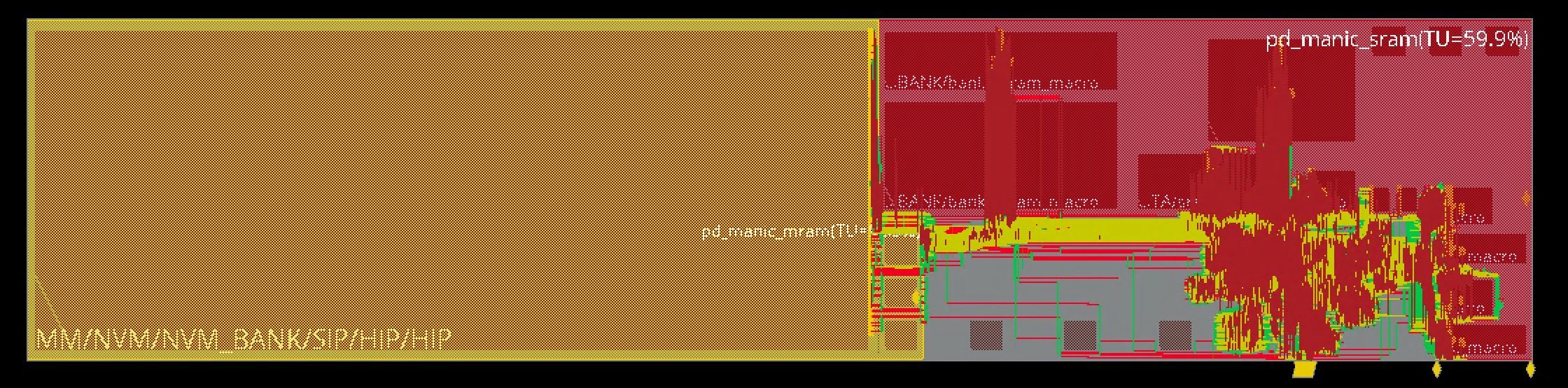

We are revisiting system design across the stack, from runtime systems to compilers to ISA to microarchitecture, to dramatically improve energy-efficiency and enable sophisticated on-device computation. Our Sonic software system enables energy-efficient machine learning while tolerating frequency power failures (ASPLOS’19), and our programmable MANIC architecture eliminates most of the wasted energy in a conventional microcontroller through a new execution model called vector-dataflow execution (MICRO’19). This project is building real prototypes, as shown above in our energy-harvesting demo for Sonic, and shown in the image below for our upcoming tape-out of the MANIC architecture in Intel 22nm FFL.

SNAFU (ISCA’21) implements the vector-dataflow model across a spatial fabric to further reduce energy. SNAFU is the first framework to generate ultra-low-power coarse-grained reconfigurable arrays (CGRAs) that are optimized from the ground-up to minimize energy while maximizing flexibility — both design-time flexibility in hardware and run-time flexibility in software. SNAFU allows the designer to easily customize processing elements via its “bring-your-own-functional-unit” (BYOFU) approach. To maximize run-time flexibility in software, SNAFU provides an extensible compiler that targets generated CGRA hardware. SNAFU consumes between 120 µW and 324 µW, depending on workload, achieving an estimated 305 MOPs/mW, and comes within 2X-3X of ASIC energy.

This project is a collaboration with Brandon Lucia.

CORGi Members

Publications

Towards Understanding the Carbon Impact in End-to-end Sensing Pipelines [pdf]

Harsh Desai, Sara McAllister, Nathan Beckmann, Brandon Lucia. HotEthics at ASPLOS 2024.

Pipestitch: An energy-minimal dataflow architecture with lightweight threads [pdf]

Nathan Serafin, Souradip Ghosh, Harsh Desai, Nathan Beckmann, Brandon Lucia. MICRO 2023.

Dataflow Blocks: Modular Time-Multiplexing for CGRAs [pdf]

Xuesi Chen, Nishanth Subramanian, Karthik Ramanathan, Nathan Beckmann, Brandon Lucia. YArch at ASPLOS 2023.

MANIC: A 19µW @ 4MHz, 256 MOPS/mW, RISC-V Microcontroller with Embedded MRAM Main Memory and Vector-Dataflow Co-Processor in 22nm Bulk FinFET CMOS [pdf]

Graham Gobieski, Oguz Atli, Cagri Erbagci, Ken Mai, Nathan Beckmann, Brandon Lucia. ISCAS 2023.

RipTide: A programmable, energy-minimal dataflow compiler and architecture [pdf]

Graham Gobieski, Souradip Ghosh, Marijn Heule, Todd Mowry, Tony Nowatzki, Nathan Beckmann, Brandon Lucia. MICRO 2022.

SNAFU: An Ultra-Low-Power, Energy-Minimal CGRA-Generation Framework and Architecture [pdf]

Graham Gobieski, Oguz Atli, Ken Mai, Brandon Lucia, Nathan Beckmann. ISCA 2021.

The Role of Edge Offload for Hardware-Accelerated Mobile Devices [pdf]

Mahadev Satyanarayanan, Nathan Beckmann, Grace A. Lewis, Brandon Lucia. HotMobile 2021.

MANIC: An Energy-Efficient Architecture for Ultra-Low-Power Embedded Systems [pdf]

Graham Gobieski, Amolak Nagi, Nathan Serafin, Mehmet Meric Isgenc, Nathan Beckmann, Brandon Lucia. MICRO 2019.

Intelligence Beyond the Edge: Inference on Intermittent Embedded Systems [pdf]

Graham Gobieski, Brandon Lucia, Nathan Beckmann. ASPLOS 2019.

Intermittent Deep Neural Network Inference [pdf]

Graham Gobieski, Nathan Beckmann, Brandon Lucia. SysML 2018.